시정수 τ = RC 라고 표현합니다. 여기서 R은 저항값이고, C는 커패시터값을 의미합니다. 저항과 커패시터로 시간을 표현할 수 있다니? 굉장히 신기하지 않을 수 없습니다.

나무위키에서 시정수의 정의를 보면 "전기회로에 갑자기 전압을 가했을 경우 전류는 점차 증가하여 마침내 일정한 값에 도달한다. 이 때의 증가의 비율을 나타내는 것으로, 정상값의 63.2%에 달할 때까지의 시간을 초로 표시한다. 전압을 제거했을 때도 이 반대가 성립된다." 와 같이 설명이 나와 있습니다. 오 그럼, 어떤 배터리를 63.2%까지 충전하는데 걸리는 시간이 저항값과 커패시터값에 의해 결정되는구나? 라고 이해할 수 있습니다. 하지만, 이런 설명만 보고 정확히 이해하기에는 정보가 조금 부족합니다. 굉장히 추상적으로 다가올 수 있죠.

시정수를 이해하려면 먼저 커패시터의 충방전 원리에 대해 알아야 합니다. 충방전 원리를 이해하는데 가장 중요한 수식은 커패시터의 전압과 전류에 관한 수식 1), 2) 입니다.

수식 1)

커패시터는 두 개의 도체판과 그 사이 일종의 절연체인 유전체로 이뤄져있기 때문에 두 개의 도체 사이는 기본적으로 전류가 흐르지 않습니다. 하지만 전압의 변화가 있을 때는 수식 1)과 같이 전류가 흐를 수 있게됩니다.

그림 1의 펄스 파형이 RC회로의 입력으로 인가될 경우 펄스파형의 Rising/Falling time 동안 커패시터에 걸리는 전압의 변화가 발생하고, 이 변화는 수식 1)과 같이 전류 ic를 발생시킵니다. 이 ic에 의해 커패시의 전압이 Vc만큼 충전과 방전이 일어납니다. Rising/Falling time 동안 급격하게 전압이 바뀌기 때문에 전류 ic역시 급격하게 증가했다가 서서히 감소합니다. 따라서, 커패시터가 충전되는 전압 Vc 역시 초반에 급격한 기울기로 충전되고 시간이 지남에 따라 서서히 기울기가 줄어듭니다. 이를 수식 2)와 같이 시간에 따라 변화하는 수식으로 표현할 수 있습니다.

수식 2)

수식 2)는 그림 1의 RC 회로를 키르히호프의 전압 법칙을 이용하면 구할 수 있고, 이를 설명한 자료는 굉장히 많으니까 여기서는 생략합니다.

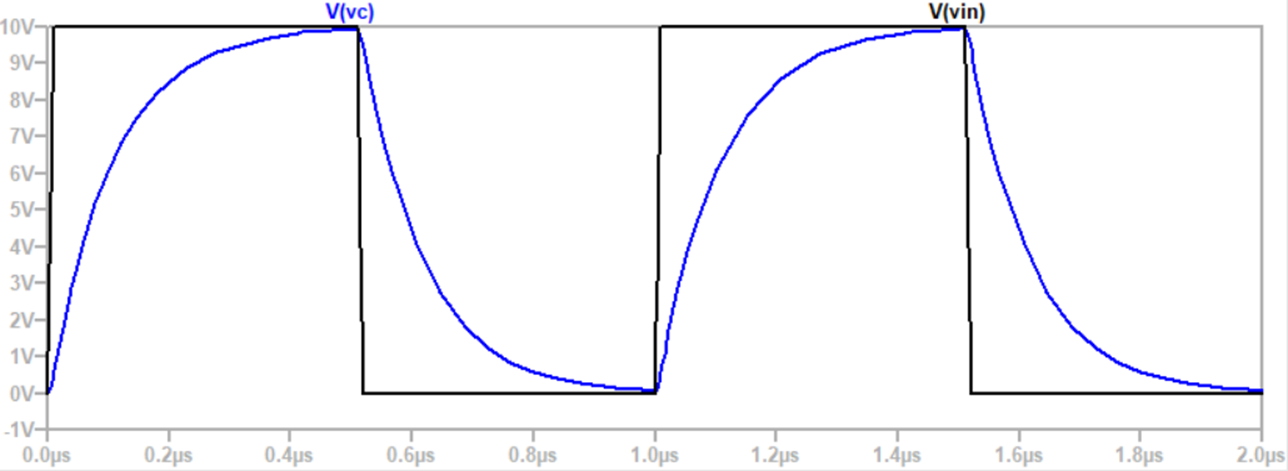

위에서 설명한 내용을 시뮬레이션으로 직접 검증해 봅시다. 그림 2 좌측의 RC 회로를 구성하고, 우측의 0us~1us동안의 시뮬레이션 결과를 보면 입력 파형 Vin(검은색 그래프)의 Rising 동안 전류 ic(빨간색 그래프)의 급격한 흐름이 발생하고 서서히 줄어듭니다. 그러면 커패시터의 전압 Vc(파란색 그래프) 역시 초반에 빠른 기울기로 증가하다가 전류가 줄어드는 만큼 충전되는 기울기가 점점 줄어듭니다. 즉, 수식 2)와 같이 exponential 함수에 따라 커패시터 충전 전압 Vc의 값이 변화하는 것을 알 수 있습니다.

이는 1us~2us동안의 커패시터 방전도 동일한 원리로 설명할 수 있습니다.

자, 이제 처음 소개했던 시정수 τ = RC의 의미를 조금 더 자세하게 알아 봅시다. 이를 위해, 그림 2의 시뮬레이션 결과에서 Vc의 전압만 따로 가져와서 그림 3 같이 확대해 봅니다.

그림 2에서 R=100ohm, C=1nF 을 사용했기 때문에 시정수 τ =RC=0.1us가 됩니다. 즉, 0.1us 동안 63.2%가 충전 되므로 입력 전압 10V의 63.2%인 6.32V가 충전 됩니다. 즉, 시정수란 커패시터의 전압이 63.2%만큼 충전됐을 때의 시간을 의미합니다. 방전 상황일 때는 커패시터의 전압이 최대 충전 전압 기준 36.8%가 되는 시점을 τ 라고 표현할 수 있습니다.

여기서 추가적으로 시정수를 2배, 3배, 4배..로 늘려보면 수식 2)에 의해 다음과 같이 충전되는 퍼센티지를 확인할 수 있습니다. 2τ는 86.5%, 3τ는 95%, 4τ는 98.2%, 5τ는 99.3%가 되므로 약 5τ가 되는 시점에서 99%이상 충전되는 것을 알 수 있습니다. 방전시에는 2τ는 13.5%, 3τ는 5%, 4τ는 1.8%, 5τ는 0.7%가 되고, 5τ이하 일 때, 1%이하의 전압이 되는 것을 알 수 있습니다.

자, 그럼 이 시정수를 실전에서 어떻게 활용할 수 있는지 예시를 한 번 들어 보겠습니다. MCU와 임의의 IC 사이에 I2C든 SPI든 약 1MHz 주기로 어떤 통신을 한다고 가정하면 GPIO 핀의 플로팅 상태를 제거하기 위해 풀업 저항을 사용해야 합니다. 그림 4와 같이 회로를 구성해 봅시다.

위 회로의 시정수 τ = Rp x Cp에 의해 결정됩니다. Cp는 MCU 데이터시트에서 제공하며, 여기서는 임의로 10pF이라고 가정 합니다. 사용자가 누설 전류를 줄이기 위해 Rp를 크게 하기 위해 20kohm으로 설정했다고 가정하면 시정수 τ =20kohm x 10pF = 200ns가 됩니다. 앞서 충전이 거의 완료되는 시점(충전 전압 99% 이상)이 5τ라고 했는데요. 이 경우 5τ는 1000ns인데 1MHz의 신호가 0~500ns동안만 High를 유지하기 때문에 충전이 다 되지 않은 상태에서 방전이 이뤄지게 됩니다. 이를 시뮬레이션 해보면 그림 5와 같습니다.

통신 신호로 이런 신호를 사용하게 될 경우 신호를 제대로 수신하지 못하는 문제가 발생합니다. 따라서, 풀업 저항 값을 조절해야 합니다. 만약 풀업 저항 Rp를 10kohm으로 줄이면 τ = 100ns가 되고, 5τ = 500ns이므로 1MHz의 신호가 High일 동안 완전 충전이 이뤄질 수 있다는 걸 알 수 있습니다. 이를 시뮬레이션으로 확인하면 그림 6과 같습니다.

그래서 최소한 10kohm보다 작은 풀업 저항을 사용해야 겠다는 사실을 알 수 있습니다. 일반적으로 4.7kohm을 풀업 저항으로 많이 사용하는 이유이기도 합니다.

그럼 여기까지 시정수에 대한 포스팅을 마칩니다~!

(풀업 풀다운 저항에 대해 더 자세히 알고 싶은 분은 아래 링크를 참고해 주세요.)

2023.07.13 - [아날로그 회로] - #11. 풀업, 풀다운 저항을 쉽게 이해해보자

#11. 풀업, 풀다운 저항을 쉽게 이해해보자

풀업 저항과 풀다운 저항은 정말 굉장히 많이 들어봤을 거에요. 회로 설계에 있어서 너무너무 기본이 되는 저항 입니다. 실무를 하다보면 자연스럽게 이해가 되는 내용이기도 하지만 처음 접하

analog-circuit-design.tistory.com

2023.07.27 - [아날로그 회로] - #11-1. 풀업, 풀다운 저항은 얼마를 달아야 할까?

#11-1. 풀업, 풀다운 저항은 얼마를 달아야 할까?

2023.07.13 - [아날로그 회로] - #11. 풀업, 풀다운 저항을 쉽게 이해해보자 #11. 풀업, 풀다운 저항을 쉽게 이해해보자 풀업 저항과 풀다운 저항은 정말 굉장히 많이 들어봤을 거에요. 회로 설계에 있

analog-circuit-design.tistory.com

'아날로그 회로' 카테고리의 다른 글

| #20. LDO(Low Drop-Out) Regulator 동작 원리 이해하기 (8) | 2023.11.26 |

|---|---|

| #19. 커패시터(Capacitor)의 종류 (2) | 2023.11.18 |

| #18. 슬루율(Slew Rate) 쉽게 이해하기! (3) | 2023.08.19 |

| #17. MOSFET의 동작 영역에 대해 쉽게 이해하기 (0) | 2023.08.15 |

| #15. 제너 다이오드 (Zenor Diode)를 이용한 보호회로 설계 (1) | 2023.07.30 |

| #11-1. 풀업, 풀다운 저항은 얼마를 달아야 할까? (15) | 2023.07.27 |

| #14-1. 디커플링 커패시터 최적 위치 배치하기 (4) | 2023.07.25 |

| #14. Decoupling Capacitor (디커플링 커패시터) 쉽게 이해하기 (1) | 2023.07.23 |