전원부에서 MOSFET의 스위칭 동작에 의한 DC 전압을 생성하는데 스위치를 ON/OFF 할 때 마다 전류의 변화가 발생합니다. 이 전류의 변화는 기생 인덕턴스 성분에 의해 과도 전압을 발생시킵니다. 즉, 링잉 또는 공진이라고 하는 원치않는 현상이 발생하게 됩니다. 스너버 회로란 이 과도 전압의 영향성을 저감시켜주는 역할을 한다고 이해하시면 됩니다. 그림 1과 같이 5V 전원을 3.3V로 다운 시켜주는 Buck 컨버터가 있다고 합시다.

그림 1의 입력 전압 Vin이 구형파 형태로 주어질 때, Drain 노드에서의 파형은 그림 2와 같이 깨끗한 형태의 구형파가 출력됩니다. 5V를 가지고 3.3V를 만들어야 하기 때문에 PMOS가 좀 더 오래 켜져 있어야해서 duty 비는 약 70%정도가 됩니다.

실제 환경에서는 PMOS와 NMOS 각각의 Drain 노드에서 기생 인덕턴스 성분이 존재하므로 그림 1은 그림 3과 같은 형태로 모델링 할 수 있습니다. 기생 인덕턴스 성분은 보통 PCB 라인 1mm당 1nH정도 수준이기 때문에 레이아웃을 잘 했다 치고 500pH로 가정해 봅니다.

[그림 3. 기생 인덕턴스가 포함된 Buck 컨버터 회로] |

[그림 4. Drain1 노드의 파형] |

기생 인덕턴스 성분 L5, L6에 의해 그림 4에서 Dran1 노드에 링잉 현상이 추가 되는 것을 확인할 수 있습니다. 이렇게 생성된 링잉 성분은 스위칭 노이즈라고도 하며, VDD나 GND를 통해 다른 노드로 인가되므로 EMC에 악영향을 미칩니다. 이 때 링잉 주파수는 수식 1)에 의해 결정됩니다.

수식 1)

그림 3에서 기생 인덕턴스 성분만 모델링 했지만 실제 PCB의 Drain1 노드에서 GND까지의 기생 캐패시턴스 성분이 존재 합니다. 이를 1nF라고 가정하면 링잉 주파수 Fr = 225MHz가 됩니다.

그럼 이 링잉 현상이 생기는 이유를 조금 더 자세하게 살펴 봅시다. 그림 5의 PMOS가 켜지고 NMOS가 닫힐 때 기생 캐패시터 C5의 전압이 충전되면서 VDD에서 C5로 나가는 고주파성분의 전류가 생성됩니다. 이 전류의 변화량은 기생 인덕터 L3에서 과도 전압을 발생시키죠. NMOS가 켜지고 PMOS가 닫힐 때는 기생 캐패시터 C5의 전압이 방전되면서 NMOS를 거쳐 GND로 고주파 성분의 전류가 들어옵니다. 이 때 발생하는 전류의 변화량으로 인해 기생 인덕터 L7에서 과도 전압이 생성됩니다. 이렇게 기생 캐패시터 C5에 충방전 되는 현상에 의해 전류가 생성되고, 이 전류의 흐름은 기생 인덕터 L3, L7에서 과도 전압을 발생시킵니다. 해당 수식은 그림5에서 확인할 수 있습니다.

기생 인덕턴스 성분이 커질수록 과도 전압은 커지므로 PCB 레이아웃을 할 때 MOSFET의 Drain과 Inductor L2 사이의 거리를 최대한 짧게 가져가는 것이 중요합니다. 하지만 레이아웃을 잘 했음에도 불구하고, 링잉 주파수가 생길 수도 있습니다. 자, 그러면 이러한 과도 전압을 어떻게 저감할 수 있을까요? 바로 스너버 회로를 사용하면 됩니다!

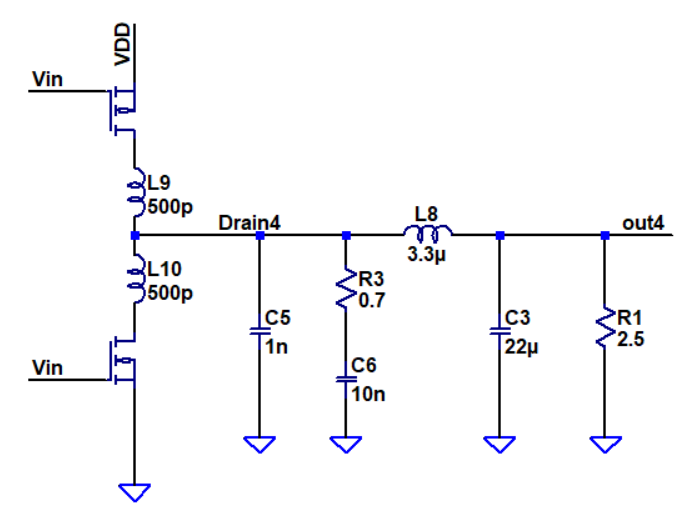

그림 5에서 기생 인덕턴스 L3, L7과 커패시턴스 C5 성분을 각각 500pH, 1nH로 가정했지만 실제 기생 성분은 알 수가 없습니다. 소자에 의한 기생 성분과 PCB의 재질, 라인의 길이 등등 영향을 미치는 요인이 굉장히 많기 때문이죠. 하지만 측정에 의해 각 기생 인덕턴스와 캐패시터를 구할 수 있습니다. Drain4 노드를 오실로스코프로 찍어보면 링잉 주파수를 확인할 수 있습니다. 그림 6의 Drain4 노드에 측정용 캐패시터 C6을 추가해서 수식 1)을 참고하여 링잉 주파수가 1/2배가 되는 값 C6을 구해봅니다. 그럼 C5+C6이 4배가 되어야 링잉 주파수 Fr이 1/2배가 되므로 기생 캐패시턴스 C5는 측정용 캐패시터 C6의 1/3에 해당합니다. 이렇게 C5를 구하고 다시 수식 1)에 대입하면 기생 인덕턴스 L3와 L7을 구할 수 있습니다.

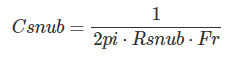

이렇게 기생 인덕턴스와 기생 캐패시턴스를 구했다면 수식 2), 3)에 의해 스너버 저항 Rsnub과 캐패시터 Csnub을 구할 수 있습니다.

수식 2)

수식 3)

수식 2), 3)에 의해서 구한 Rsnub, Csnub를 그림 6과 같이 Drain4 노드에 시리즈로 연결하면 스너버 회로가 완성 됩니다. 그림 5의 Drain3 노드 파형이 그림 7이라면, 스너버 회로가 적용된 그림 6의 Drain4 노드 파형은 그림 8과 같습니다. 즉, 스너버 회로에 의해 링잉 현상이 상당 부분 개선된 것을 확인 할 수 있습니다.

[그림 7. 기생 인덕턴스에 의한 Drain3 노드 파형] |

[그림 8. 스너버 회로에 의해 개선된 Drain4 노드 파형] |

여기까지 스너버 회로에 대한 포스팅을 마칩니다~!

'아날로그 회로' 카테고리의 다른 글

| #13. MOSFET의 구조와 회로 모델 (4) | 2023.07.18 |

|---|---|

| #12. MOSFET을 이용한 증폭기 설계 (4) | 2023.07.16 |

| #11. 풀업, 풀다운 저항을 쉽게 이해해보자 (5) | 2023.07.13 |

| #6-1. MOSFET에 붙어있는 다이오드는 뭘까? (18) | 2023.07.10 |

| #9. 역극성 방지 회로와 역전압 보호 회로 (8) | 2023.06.29 |

| #7 신호 검출용 다이오드 (Photodiode) (0) | 2023.06.21 |

| #6. 다이오드를 왜, 어디에 사용할까? - 정류 회로, 보호 회로 (1) | 2023.06.19 |

| #5. Diode의 정의와 기본적인 동작 특성 (0) | 2023.06.18 |